触发器

触发器(英语:Flip-flop, FF),中国大陆译作“触发器”、台湾及香港译作“正反器”,是一种具有两种稳态的用于储存的组件,可记录二进制数字信号“1”和“0”。触发器是一种双稳态多谐振荡器(bistable multivibrator)。该电路可以通过一个或多个施加在控制输入端的信号来改变自身的状态,并会有1个或2个输出。触发器是构成时序逻辑电路以及各种复杂数字系统的基本逻辑单元。触发器和锁存器是在计算机、通讯和许多其他类型的系统中使用的数字电子系统的基本组成部分。

触发器的线路图由逻辑门组合而成,其结构均由SR锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时序脉波(CK)之间的相互影响。这里的触发器特指flip-flop,flip-flop一词主要是指具有两个状态相互翻转,例如编程语言中使用flip-flop buffer(翻译作双缓冲)[来源请求]。

触发器的种类

编辑触发器可以分成几种常见的类型: SR (设置-重置,"set-reset"), D (数据或延迟,"data" or "delay"[1]), T(反转,"toggle"),和JK。 以上类型的触发器皆可用特征方程,以现有的输入、输出信号(Q),导出下个(即下个时钟脉冲的)输出(Qnext)。

RS触发器

编辑基本RS触发器又称SR锁存器,是触发器中最简单的一种,也是各种其他类型触发器的基本组成部分。两个与非门或或非门的输入端输出端进行交叉耦合或首尾相接,即可构成一个基本RS触发器。

当R与S皆为低电位,回授会让Q与Q(Q的反相)保持于一个固定的状态。当S(Set)为高电位,R(Reset)为低电位时,输出Q会被强制设置为高电位;相反的,当S为低电位,R为高电位时,输出Q会被强制设置为低电位。

| SR锁存器运算[2] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 状态转移表 | 激励表 | |||||||

| S | R | Qnext | 动作 | Q | Qnext | S | R | |

| 0 | 0 | Q | 保持 | 0 | 0 | 0 | X | |

| 0 | 1 | 0 | 重置 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 设置 | 1 | 0 | 0 | 1 | |

| 1 | 1 | X | 不允许的输入 | 1 | 1 | X | 0 | |

特征方程为 ,且RS=0。

D触发器

编辑D触发器有一个输入、一个输出和一个主频输入,当主频由0转为1时,输出的值会和输入的值相等。此类触发器可用于防止因为噪声所带来的错误,以及通过管线增加处理数据的数量。

真值表如下:

| D | CK | Q | Qnext |

| 0 | ↑ | X | 0 |

| 1 | ↑ | X | 1 |

| X | 0(1) | 0 | 0 |

| X | 0(1) | 1 | 1 |

JK触发器

编辑JK触发器的名称来源不明。

JK触发器设有两个输入,其输出的值由以下的算式来决定。

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0。

对应表如下:

| JK触发器运算[4] | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 状态转移表 | 激励表 | ||||||||

| J | K | CK | 动作 | Qnext | Q | Qnext | 动作 | J | K |

| 0 | 0 | ↑ | 保持 | Q | 0 | 0 | 不变 | 0 | X |

| 0 | 1 | ↑ | 重置 | 0 | 0 | 1 | 设置 | 1 | X |

| 1 | 0 | ↑ | 设置 | 1 | 1 | 0 | 重置 | X | 1 |

| 1 | 1 | ↑ | 反转 | Q | 1 | 1 | 不变 | X | 0 |

| X | X | 0(1) | 保持 | Q | |||||

T触发器

编辑T触发器(Toggle Flip-Flop,or Trigger Flip-Flop)设有一个输入和输出,当主频由0转为1时:如果输入端T为1,则输出端的状态Q发生反转;如果输入端T为0,则输出端的状态Q保持不变。把JK触发器的J和K输入点连接在一起,即构成一个T触发器。

因此T触发器的算式为:

| T触发器运算[4] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 状态转移表 | 激励表 | |||||||

| 动作 | 动作 | |||||||

| 0 | 0 | 0 | 保持(无上升沿) | 0 | 0 | 0 | 不变 | |

| 0 | 1 | 1 | 保持(无上升沿) | 1 | 1 | 0 | 不变 | |

| 1 | 0 | 1 | 反转 | 0 | 1 | 1 | 反相 | |

| 1 | 1 | 0 | 反转 | 1 | 0 | 1 | 反相 | |

同步触发器

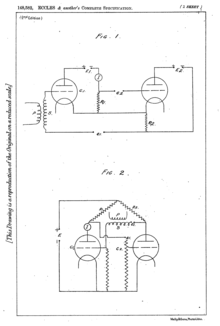

编辑主从触发器

编辑为了防止空翻现象对触发器实际工作的影响,主从结构触发器被研制出来。

主从RS触发器

编辑它由两个同步RS触发器以及一个反相器所构成。

主从JK触发器

编辑由于主从RS触发器对输入信号有所约束(R跟S不能同时为1),又开发出了主从JK触发器。

时序考量

编辑- 建立时间(setup time)是指数据在被采样时钟边沿采样到之前,需保持稳定的最小时间。

- 维持时间(hold time)是指数据在被采样时钟边沿采样到之后,需保持稳定的最小时间。

在触发器的数据手册一般会标示组件的建立时间(tsu)及维持时间(th),一般会是以纳秒(ns)为单位,有些先进的触发器可以到数百皮秒(ps)。若数据及控制输入从采样时钟边沿之前就维持定值,且时间超过建立时间,在采样时钟边沿之后就维持定值,且时间也超过维持时间,可以避免触发器的亚稳态现象。

参见

编辑参考资料

编辑- ^ Shiva, Sajjan G. Computer design and architecture 3rd. CRC Press. 2000: 81. ISBN 978-0-8247-0368-4.

- ^ Roth, Charles H. Jr. "Latches and Flip-Flops." Fundamentals of Logic Design. Boston: PWS, 1995. Print.

- ^ M Morris Mano, Michael D Ciletti. Digital design: With an Introduction to the Verilog HDL. 培生教育. 2013: 第216页. ISBN 9780273764526.

- ^ 4.0 4.1 Mano, M. Morris; Kime, Charles R. Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. 2004: pg283. ISBN 0-13-191165-1.

- Hwang, Enoch. Digital Logic and Microprocessor Design with VHDL. Thomson. 2006 [2010-02-22]. ISBN 0-534-46593-5. (原始内容存档于2008-10-12).

- Salman, E., Dasdan, A., Taraporevala, F., Kucukcakar, K., Friedman, E. Pessimism Reduction in Static Timing Analysis Using Interdependent Setup and Hold Times. Proc. of Int. Symp. on Quality Electronic Design (ISQED): 159–164. 2006. (This paper explains the interdependence of setup time, hold time, and clock-to-q delay and shows how to use it for pessimism reduction in static timing analysis.)

- Schulz, Klaus-E. Ideal pulse circuit without RC-combination and non-clocked JK flip-flops (look discussion) (PDF). 2007.[永久失效链接]

- Michael Keating, Pierre Breacaud. 片上系统——可重用设计方法学(第二版)(英文名:Reuse Methodology Manual for System-on-a-Chip Designs, Third Edition). 北京: 电子工业出版社. 2004. ISBN 7-5053-9338-3.

外部链接

编辑- FlipFlop Hierarchy, shows interactive flipflop circuits.

- The J-K Flip-Flop (页面存档备份,存于互联网档案馆)