双列直插封装

双列直插封装(英语:dual in-line package) 也称为DIP封装或DIP包装,简称为DIP或DIL[1],是一种集成电路的封装方式,集成电路的外形为长方形,在其两侧则有两排平行的金属引脚,称为排针。DIP包装的元件可以焊接在印刷电路板电镀的贯穿孔中,或是插入在DIP插座(socket)上。

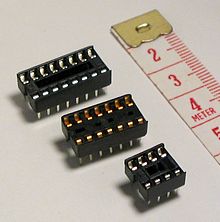

DIP包装的元件一般会简称为DIPn,其中n是引脚的个数,例如十四针的集成电路即称为DIP14,右图即为DIP14的集成电路。

应用

编辑集成电路常使用DIP包装,其他常用DIP包装的零件包括DIP开关、LED、七段显示器、条状显示器及继电器。电脑及其他电子设备的排线也常用DIP包装的接头。

使用

编辑最早的DIP包装元件是由快捷半导体公司的Bryant Buck Rogers在1964年时发明,第一个元件有14个引脚,相当类似今天的DIP包装元件[2]。其外形为长方形,相较于更早期的圆形元件,长方形元件可以提高电路板中元件的密度[3]。DIP包装的元件也很适合自动化装配设备,电路板上可以有数十个到数百个IC,利用波峰焊接机焊接所有零件,再由自动测试设备进行测试,只需要少数的人工作业。DIP元件的大小其实比其内部的集成电路大很多。在二十世纪末时表面贴装技术(SMT)包装的元件可以缩小系统的体积及重量。不过有些场合仍会用到DIP元件,例如在制作电路原型时,就会使用DIP元件配合面包板制作电路原型,方便元件的插入及移除。

DIP包装元件是1970及1980年代微电子产业的主流。在21世纪初的使用量逐渐减少,被像是PLCC及SOIC等表面贴装技术的封装所取代。表面贴装技术元件的特性适合量产时使用,但在电路原型制作时比较不便。由于有些新的元件只提供表面贴装技术封装的产品,因此有许多公司生产将SMD元件转换为DIP包装的转接器,可以将表面贴装技术封装的IC放在转接器中,像DIP包装元件一様的再接到面包板或其他配合直插式元件的电路原形板(像洞洞板)中。

对于像EPROM或是GAL之类的可编程元件而言,DIP封装的元件由于方便由外部烧录设备烧录资料(DIP封装元件可以直接插入烧录设备对应的DIP插座),仍盛行了一段时间。不过随着在线烧录(ISP)技术的普及,DIP封装元件方便烧录的好处也就不再重要。在1990年代,超过20只引脚的元件可能还有DIP封装的产品。而二十一世纪时,许多新的可编程元件已都是SMT封装,不再提供DIP封装的产品。

安装方式

编辑DIP封装元件可以用通孔插装技术的方式安装在电路板上,也可以利用DIP插座安装。利用DIP插座可以方便元件的更换,也可以避免在焊接时造成元件过热的情形。一般插座会配合体积较大或是单价较高的集成电路使用。像测试设备或烧录器等,常常需要安装及拆下集成电路的场合,会使用零抗力的插座。DIP封装元件也可以配合面包板使用,面包板一般是作为教学、开发设计或元件设计而使用。

结构

编辑双列直插封装芯片的封装一般是由塑胶或陶瓷制成。陶瓷封装的气密性良好,常用在需要高可靠度的设备。不过大部分的双列直插封装芯片都是使用热固性树脂塑胶。一个不到2分钟的固化周期,可以生产上百个的芯片。

引脚数及间距

编辑常用的DIP封装符合JEDEC标准,二引脚之间的间距(脚距)为0.1吋(2.54毫米)。二排引脚之间的距离(行间距、row spacing)则依引脚数而定,最常见的是0.3吋(7.62毫米)或0.6吋(15.24毫米)。其他较少见的距离有0.4吋(10.16毫米)或0.9吋(22.86毫米),也有一些包装是脚距0.07吋(1.778毫米),行间距则为0.3吋、0.6吋或0.75吋。

前苏联及东欧国家使用的DIP封装大致接近JEDEC标准,但脚距使用公制的2.5毫米,而不是来自英制的0.1吋(2.54毫米)。

DIP封装的引脚数恒为偶数。若行间距为0.3吋,常见的引脚数为8至24,偶尔也会看到引脚数为4或28的包装。若行间距为0.6吋,常见的引脚数为24、28、32或40,也有引脚数为36、48或52的包装。摩托罗拉 68000及Zilog Z180等CPU的引脚数为64,这是常用DIP封装的最大引脚数[4]。

方向和引脚编号

编辑如右图所示,当元件的识别缺口朝上时,左侧最上方的引脚为引脚1,其他引脚则以逆时针的顺序依序编号。有时引脚1也会以圆点作为标示。

例如DIP14的IC,识别缺口朝上时,左侧的引脚由上往下依序为引脚1至7,而右侧的引脚由下往上依序为引脚8至14。

其他衍生的封装

编辑SOIC(Small Outline IC)是一种很常用的表面贴装技术封装方式,特别常在消费性电子及个人电脑中使用。SOIC可视为是标准IC的PDIP封装的缩小版,其排针也是在元件的二侧。而SOJ(Small Outline J-lead)及SOP(Small Outline Package)系列的封装方式也是和DIP封装类似的表面贴装技术封装方式。

相关条目

编辑参考资料

编辑- ^ see for instance (PDF). [2012-02-25]. (原始内容 (PDF)存档于2020-09-30).

- ^ Dummer, G.W.A. Electronic Inventions and Discoveries 2nd ed. Pergamon Press ISBN 0-08-022730-9

- ^ http://www.computerhistory.org/semiconductor/timeline/1965-Package.html (页面存档备份,存于互联网档案馆) Computer Museum retrieved April 16, 2008

- ^ Kang, Sung-Mo; Leblebici, Yusuf. CMOS digital integrated circuits (3rd Edition). McGraw-Hill. 2002: 42. ISBN 0072460539.