印制电路板

此条目需要补充更多来源。 (2016年11月14日) |

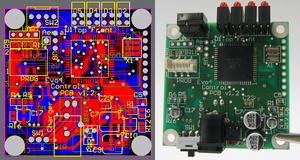

印刷电路板,又称印制电路板,印刷线路板,常用英文缩写PCB(Printed circuit board)或PWB(Printed wire board),是电子元件的支撑体,在这其中有金属导体作为连接电子元器件的线路。

传统的电路板,采用印刷蚀刻阻剂的工法,做出电路的线路及图面,因此被称为印刷电路板或印刷线路板。由于电子产品不断微小化跟精细化,目前大多数的电路板都是采用贴附蚀刻阻剂(压膜或涂布),经过曝光显影后,再以蚀刻做出电路板。

pcb[1] (页面存档备份,存于互联网档案馆)最早使用的是纸基覆铜印制板。自半导体晶体管于20世纪50年代出现以来,对印制板的需求量急剧上升。特别是集成电路的迅速发展及广泛应用,使电子设备的体积越来越小,电路布线密度和难度越来越大,这就要求印制板要不断更新。目前印制板的品种已从单面板发展到双面板、多层板和挠性板;结构和质量也已发展到超高密度、微型化和高可靠性程度;新的设计方法、设计用品和制板材料、制板工艺不断涌现。

历史

编辑在印制电路板出现之前,电子元件之间的互连都是依靠电线直接连接而组成完整的线路。现在,电路面包板只是作为有效的实验工具而存在,而印刷电路板在电子工业中已经成了占据绝对统治的地位。

20世纪初,人们为了简化电子机器的制作,减少电子零件间的配线,降低制作成本等优点,于是开始钻研以印刷的方式取代配线的方法。三十年间,不断有工程师提出在绝缘的基板上加以金属导体作配线。而最成功的是1925年,美国的 Charles Ducas 在绝缘的基板上印刷出线路图案,再以电镀的方式在绝缘基材上印刷出导体线路图案,称为加成法。[1][2]

直至1936年,奥地利人保罗·爱斯勒(Paul Eisler)在英国发表箔膜技术[1],他在一个收音机装置内采用了印刷电路板;而在日本,宫本喜之助以喷附配线法[3]成功申请专利。[4]而两者中 Charles Ducas、宫本喜之助的做法是只加上所需的配线;而Paul Eisler的方法与现今的印刷电路板最为相似,即在覆盖金属箔的绝缘基板上选择性涂覆抗蚀剂,刻蚀掉非必要铜区制备电子线路,这类做法称为减去法。[2]虽然如此,但因为当时的电子零件发热量大,两者的基板也难以配合使用,以致未有正式的实用作,不过也使印刷电路技术更进一步。[1]

1941年,美国在滑石上漆上铜膏作配线,以制作近接信管。1943年,美国人将该技术大量使用于军用收音机内。1947年,环氧树脂开始用作制造基板。同时美国国家标准局开始研究以印刷电路技术形成线圈、电容器、电阻器等制造技术。1948年,美国正式认可这个发明用于商业用途。自20世纪50年代起,发热量较低的晶体管大量取代真空管的地位,印刷电路版技术才开始被广泛采用,当时以蚀刻箔膜技术为主流[1]。1950年,日本使用玻璃基板上以银漆作配线;和以酚醛树脂制的纸质酚醛基板(CCL)上以铜箔作配线。[1]1951年,聚酰亚胺的出现,使树脂的耐热性再进一步,也制造聚亚酰胺基板。[1]1953年,Motorola开发出电镀贯穿孔法的双面板。这方法也应用到后期的多层电路板上。[1]印刷电路板广泛被使用10年后的60年代,其技术也日益成熟。而自从Motorola的双面板问世,多层印刷电路板(Multi-Layer Board,MLB)开始出现,使配线与基板面积比更为提高。

1960年,V. Dahlgreen以印有电路的金属箔膜贴在热可塑性的塑胶中,造出软性印刷电路板。[1] 1961年,美国的Hazeltine Corporation参考电镀贯穿孔法,制作出多层板。[1]1967年,发表增层法之一的“Plated-up technology”。[1][5]1969年,FD-R以聚酰亚胺制造软性印刷电路板。[1]1979年,Pactel发表增层法之一的“Pactel法”。[1]1984年,NTT开发薄膜回路的“Copper Polyimide法”。[1]1988年,西门子公司开发Microwiring Substrate的增层印刷电路板。[1]

1990年,IBM开发“表面增层线路”(Surface Laminar Circuit,SLC)的增层印刷电路板。[1]1995年,松下电器开发ALIVH的增层印刷电路板。[1] 1996年,东芝开发B2it的增层印刷电路板。[1]就在众多的增层印刷电路板方案被提出的1990年代末期,增层印刷电路板也正式大量地被实用化。

21世纪初前后, 积层法MLB和挠性印制电路板(Flexible PrintedCircuit,FPC)快速发展,片式元器件小型化以及高密度安装方式,提高了电子产品互连密度。21世纪20年代,印制电路板向着高输入/输出(Input/Ouput,I/O)密度、高精细度(窄线宽/ 线距,Line/Space,L/S)、高集成度不断演进,呈现一体化集成和三维安装的特征。[2]

制造印刷电路板

编辑基材

编辑基材普遍是以基板的绝缘及强化部分作分类,常见的原料为电木板、玻璃纤维板,以及各式的塑胶板。而PCB的制造商普遍会以一种以玻璃纤维不织物料以及环氧树脂组成的绝缘预浸渍材料(prepreg),再以和铜箔压制成铜箔基板备用。

而常见的基材及主要成分有:

- FR-1 ──酚醛棉纸,这基材通称电木板(比FR-2较高经济性)

- FR-2 ──酚醛棉纸,

- FR-3 ──棉纸、环氧树脂

- FR-4 ──玻璃布(Woven glass)、环氧树脂

- FR-5 ──玻璃布、环氧树脂

- FR-6 ──毛面玻璃、聚酯

- G-10 ──玻璃布、环氧树脂

- CEM-1 ──棉纸、环氧树脂(阻燃)

- CEM-2 ──棉纸、环氧树脂(非阻燃)

- CEM-3 ──玻璃布、环氧树脂

- CEM-4 ──玻璃布、环氧树脂

- CEM-5 ──玻璃布、多元酯

- AlN ──氮化铝

- SIC ──碳化硅

金属涂层

编辑金属涂层除了有基板上的配线外,也可以是基板线路跟电子元件焊接的地方。此外,由于不同的金属价格不同,因此直接影响生产的成本。另外,每种金属的可焊性、接触性,电阻阻值等等不同,这也会直接影响元件的效能。

常用的金属涂层有:

线路设计

编辑印制电路板的设计是以电路原理图为蓝本,实现电路使用者所需要的功能。印刷电路板的设计主要指版图设计,需要内部电子元件、金属连线、通孔和外部链接的布局、电磁保护、热耗散、串音等各种因素。优秀的线路设计可以节约生产成本,达到良好的电路性能和散热性能。简单的版图设计可以用手工实现,但复杂的线路设计一般也需要借助计算机辅助设计(CAD)实现,而著名的设计软件有OrCAD、Pads (也即PowerPCB)、Altium designer(也即Protel)、FreePCB、CAM350、AutoCAD以及开源软件KiCad等。

电路板的基本组成

编辑目前的电路板,主要由以下组成

- 线路与图面(Pattern):线路是做为原件之间导通的工具,在设计上会另外设计大铜面作为接地及电源层。线路与图面是同时做出的。

- 介电层(Dielectric):用来保持线路及各层之间的绝缘性,俗称为基材

- 孔(Through hole / via):导通孔可使两层次以上的线路彼此导通,较大的导通孔则做为零件插件用,另外有非导通孔(nPTH)通常用来作为表面贴装定位,组装时固定螺丝用

- 防焊油墨(Solder resistant /Solder Mask) :并非全部的铜面都要吃锡上零件,因此非吃锡的区域,会印一层隔绝铜面吃锡的物质(通常为环氧树脂),避免非吃锡的线路间短路。根据不同的工艺,分为绿油、红油、蓝油。

- 丝印(Legend /Marking/Silk screen):此为非必要的结构,主要的功能是在电路板上标注各零件的名称、位置框,方便组装后维修及辨识用。

- 表面处理(Surface Finish):由于铜面在一般环境中,很容易氧化,导致无法上锡(焊锡性不良),因此会在要吃锡的铜面上进行保护。保护的方式有喷锡(HASL),化金(ENIG),化银(Immersion Silver),化锡(Immersion Tin),有机保焊剂(OSP),方法各有优缺点,统称为表面处理。

基本制作

编辑根据不同的技术可分为消除和增加两大类过程。

减去法

编辑减去法(Subtractive),是利用化学品或机械将空白的电路板(即铺有完整一块的金属箔的电路板)上不需要的地方除去,余下的地方便是所需要的电路。

- 丝网印刷:把预先设计好的电路图制成丝网遮罩,丝网上不需要的电路部分会被蜡或者不透水的物料覆盖,然后把丝网遮罩放到空白线路板上面,再在丝网上油上不会被腐蚀的保护剂,把线路板放到腐蚀液中,没有被保护剂遮住的部分便会被蚀走,最后把保护剂清理。

- 感光板:把预先设计好的电路图制在透光的胶片遮罩上(最简单的做法就是用打印机印出来的投影片),同理应把需要的部分印成不透明的颜色,再在空白线路板上涂上感光颜料,将预备好的胶片遮罩放在电路板上照射强光数分钟,除去遮罩后用显影剂把电路板上的图案显示出来,最后如同用丝网印刷的方法一样把电路腐蚀。

- 刻印:利用铣床或激光雕刻机直接把空白线路上不需要的部分除去。

加成法

编辑加成法(Additive),现在普遍是在一块预先镀上薄铜的基板上,覆盖光阻剂(D/F),经紫外光曝光再显影,把需要的地方露出,然后利用电镀把线路板上正式线路铜厚增厚到所需要的规格,再镀上一层抗蚀刻阻剂-金属薄锡,最后除去光阻剂(这制程称为去膜),再把光阻剂下的铜箔层蚀刻掉。

半加成法

编辑半加成法是在基材绝缘介质表面,首先沉积一层薄铜,然后在其上覆盖抗蚀剂,选择性遮盖非目标区域,之后再利用电镀沉积一层厚铜,最后除去抗蚀剂和闪蚀掉薄层基铜完成电子线路构建。[2]

多层制作

编辑积层法

编辑[1] 积层法是制作多层印刷电路板的方法之一。是在制作内层后才包上外层,再把外层以减去法或加成法所处理。不断重复积层法的动作,可以得到再多层的多层印刷电路板则为顺序积层法。

- 内层制作

- 积层编成(即黏合不同的层数的动作)

- 积层完成(减去法的外层含金属箔膜;加成法)

- 钻孔

- 减去法

- Panel电镀法

- 全块PCB电镀

- 在表面要保留的地方加上阻绝层(resist,防止被蚀刻)

- 蚀刻

- 去除阻绝层

- Pattern电镀法

- 在表面不要保留的地方加上阻绝层

- 电镀所需表面至一定厚度

- 去除阻绝层

- 蚀刻至不需要的金属箔膜消失

- Panel电镀法

- 加成法

- 令表面粗糙化

- 完全加成法(full-additive)

- 在不要导体的地方加上阻绝层

- 以无电解铜组成线路

- 部分加成法(semi-additive)

- 以无电解铜覆盖整块PCB

- 在不要导体的地方加上阻绝层

- 电解镀铜

- 去除阻绝层

- 蚀刻至原在阻绝层下无电解铜消失

- 减去法

增层法

编辑增层法是制作多层印刷电路板的方法之一,顾名思义是把印刷电路板一层一层的加上。每加上一层就处理至所需的形状。

ALIVH

编辑ALIVH(Any Layer Interstitial Via Hole,Any Layer IVA)是日本松下电器开发的增层技术。这是使用芳香聚酰胺(Aramid)纤维布料为基材[1]。

- 把纤维布料浸在环氧树脂成为“黏合片”(prepreg)

- 激光钻孔

- 钻孔中填满导电膏

- 在外层黏上铜箔

- 铜箔上以蚀刻的方法制作线路图案

- 把完成第二步骤的半成品黏上在铜箔上

- 积层编成

- 再不停重复第五至七的步骤,直至完成

B2it

编辑B2it(Buried Bump Interconnection Technology)是东芝开发的增层技术。

- 先制作一块双面板或多层板

- 在铜箔上印刷圆锥银膏

- 放黏合片在银膏上,并使银膏贯穿黏合片

- 把上一步的黏合片黏在第一步的板上

- 以蚀刻的方法把黏合片的铜箔制成线路图案

- 再不停重复第二至四的步骤,直至完成

注文

编辑"FirstPCB"[失效链接] "Seeed Studio" (页面存档备份,存于互联网档案馆) "Elecrow" (页面存档备份,存于互联网档案馆) "Makerfabs" (页面存档备份,存于互联网档案馆) "PCBONLINE" (页面存档备份,存于互联网档案馆)

产业现状

编辑由于印制电路板的制作处于电子设备制造的后半程,因此被称为电子工业的下游产业。几乎所有的电子设备都需要印制电路板的支援,因此印制电路板是全球电子元件产品中市场占有率最高的产品。目前日本、中国大陆、台湾、西欧和美国为主要的印制电路板制造基地。

PCB设计软件

编辑参见

编辑参考文献

编辑- ^ 1.00 1.01 1.02 1.03 1.04 1.05 1.06 1.07 1.08 1.09 1.10 1.11 1.12 1.13 1.14 1.15 1.16 1.17 1.18 1.19 增层、多层印刷电路板技术 ISBN 957-21-3192-3

- ^ 2.0 2.1 2.2 2.3 Li, Peng; Yu, Junyi; Luo, Suibin; Lai, Zhiqiang; Xiao, Bin; Yu, Shuhui; Sun, Rong. Cu deposition technologies for build-up film substrates towards FC-BGA. SCIENTIA SINICA Chimica. 2023-10-01, 53 (10). ISSN 1674-7224. doi:10.1360/SSC-2023-0130 (英语).

- ^ メタリコン法吹着配線方法(特許119384号)

- ^ 《4.2 積層体の構造の概要》-[[日本專利局]](特許庁) (PDF). [2008-06-15]. (原始内容 (PDF)存档于2011-03-23).

- ^ R.L. Beadles: Interconnections and Encapsulation, AD 654-630, vol.14 of "Integrated Silicon Device Technology" ASD-IRD-63-316, Research Triangle Institute, 1967, May

- ^ 6.0 6.1 6.2 魏雄。《PowerPCB 5.0.1 印制电路板设计与实践》北京:电子工业出版社,2006年10月,3-4。 ISBN 7-121-03298-8