多閘極電晶體

多閘極電晶體(英語:Mulitgate Device)是指集合了多個閘極於一體的金屬氧化物半導體場效電晶體(MOSFET)。它可以用一個電極來同時控制多個閘極,亦可用多個電極單獨控制各閘極。後者有時又被叫做Multiple Independent Gate Field Effect Transistor(MIGFET)。多閘極電晶體被提出為的是克服半導體工業裡摩爾定律(Moore's law)發展至今體積的縮小已經到達物理極限的難題。[1]

相當多的公司和機構已經在積極發展多閘極電晶體,其中包含了超微半導體、日立、IBM、英飛凌、英特爾、台積電、飛思卡爾、加州大學伯克利分校等等,而ITRS預估多閘極電晶體將是32奈米以下重要的奠基石。[2]實現上主要的障礙來自於製造技術,不論是平面和非平面的設計都面臨挑戰,特別是顯影以及圖案化技術。其他伴隨發展的包含了通道應力、矽上絕緣(SOI)以及高介電質/金屬閘極材料。

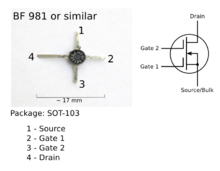

雙閘極電晶體廣泛用於超高頻混頻器(VHF mixers)和超高頻前端放大器(VHF front end amplifiers)。製造商包含Motorola、NXP和Hitachi。[3][4][5]

工業需求

編輯平面電晶體主導了整個半導體工業已經好長一段時間。隨著尺寸愈做愈小,出現了短通道效應,特別是漏電流,這類使得元件耗電的因素。

多閘極電晶體的載子通道受到接觸各平面的閘極控制。因此提供了一個更好的方法可以控制漏電流。由於多閘極電晶體有更高的本徵增益和更低的溝道調製效應,在類比電路領域也能夠提供更好的效能。如此可以減少耗電量以及提升晶片效能。立體的設計也可以提高電晶體密度,進而發展需要高密度電晶體的微機電領域。

挑戰

編輯如何將非平面電晶體相容於傳統平面電晶體的製程所面臨的挑戰包含:

- 製造僅有10納米左右的矽「鰭」

- 製造與矽鰭各面接觸的合適閘極

變形

編輯文獻裡也有其他多種不同的設計。一般來說可分為平面和非平面,以及不同的通道和閘極數(2、3或4)。

平面雙閘極電晶體

編輯平面雙閘極電晶體使用傳統平面(層層堆疊)的工藝過程來製造此雙閘極元件,避免為了製造非平面、垂直的電晶體結構而必須引入更為複雜的顯影設備。在平面雙閘極電晶體裡,源極/汲極通道像三明治一樣被包裹在兩個獨立的氧堆疊閘極之間。建造這種結構的困難處在於如何讓上下兩個閘極能夠自動地彼此對準。

FlexFET

編輯FlexFET是一種平面獨立雙閘極電晶體,它的上閘極部分是金屬鑲嵌閘極的MOSFET,下閘極部分則是深埋在閘極溝槽裡且自對準的JFET。

FlexFET是一個真正的雙閘極電晶體,其原因是(1)上下兩個閘極都可對電晶體進行操作,以及(2)上下兩個閘極的操作是彼此互相影響的。FlexFET正在發展當中且已經被美國半導體公司生產出來。

FinFET

編輯FinFET這詞是由美國加州大學伯克利分校胡正明、劉金智潔(Tsu-Jae King-Liu)[6]、傑佛瑞·波克(Jeffrey Bokor)等3位教授所命名,用來描述一種基於早期DELTA(單閘極)電晶體的設計演化出來並建立在矽上絕緣基板上的非平面雙閘極電晶體。FinFET主要的特色在於將導電通道包裹在矽「鰭」裡面。源極和汲極之間的距離決定了這個元件的等效通道長度。

現在對FinFET這詞的使用已經愈來愈模糊。微處理器廠商AMD、IBM、Motorola也把他們的雙閘極元件叫做FinFET,而Intel卻避免用這個詞來稱呼他們與此相像的三閘極電晶體。一般來說,FinFET被用在那些有「鰭」特徵的電晶體上,並不在乎它確實有幾個閘極存在。

2002年台積電製造出操作電壓僅0.7伏特的25納米電晶體。它的設計之後被命名為「Omega FinFET」,取自於它的閘極包裹住源極/汲極結構,其形狀類似希臘字母omega(Ω)。對N型電晶體來說,它的閘極延遲僅有0.39皮秒(縮寫ps),而對P型電晶體來說,僅有0.88ps。

FinFET可以設計成兩個單獨可控制閘極,這可以讓電晶體的設計更為彈性,可以製造出更具效能、低耗電的元件。

2012年開始,Intel開始用FinFETs作為他們未來的商品。最近的消息透露,Intel的電晶體有不同於一般使用矩形的三角形結構,據推測是因為三角形比矩形有較高的結構強度,有助於提高製造的可靠度,而另一方面則是三角柱的面與體積的比例相對立方體來說來的大,這有助於提升開關性能。

2012年九月,GlobalFoundries宣布在2014年開始提供23納米FinFET。隔一個月,它的競爭對手,台積電2013年11月開始生產16納米FinFETs。

三閘極電晶體

編輯三閘極電晶體(Tri-gate)被Intel使用在自家的Ivy Bridge和Haswell處理器上。此元件將一個閘極堆疊在兩個垂直放置的閘極上面,此電子多了三倍的可移動面積。Intel宣稱他們的三閘極電晶體可以減少漏電流進而減少耗能。相對之前的產品而言,此元件可提高35%的速度並且僅需一半的耗電量。

Intel表示,"多出來的控制閘極允許我們在'開啟'狀態時盡可能增加電流量(以增進效能),和在'關閉'狀態時讓電流量趨近於零(減少耗能),並且可以讓電晶體狀態之間的轉換速度變得更快(同樣,可以增加效能)。Intel已經表明在Sandy Bridge之後的處理器都將基於此3D設計。

Intel是全世界第一個發表此項技術的廠商。在2002年九月,Intel宣稱此元件"可最大化增加轉換速度請減少耗電電流"。一年之後的2003年九月,AMD在一場國際固態元件和材料的研討會上宣布他們也在做類似的設計。至此之後就沒有其他消息,直至在2011年的英特爾開發者論壇(IDF 2011)上展示以他們在IDF2009年發表的技術製造的靜態隨機存取記憶體(SRAM chip)。

2012年4月23日,Intel建造了一個新的產線,命名為Ivy Bridge,主要生產三閘極電晶體。Intel自2002年就開始發展三閘極電晶體結構,但在2011年才正式量產。此種新型態電晶體在舊金山2011年4月4號被提出討論。Intel產線端預計在2011年和2012年改良後可以開始生產Ivy Bridge中央處理器。除了在桌上型電腦內的Ivy Bridge中央處理器使用外,此元件也被使用在低功率的Atom晶片上。

"三閘極電晶體"一詞有時也被廣泛用來指在任何有三個有效閘極或通道的電晶體。

GAA FET

編輯閘極全環電晶體(Gate-all-around,GAAFET),或稱為「環繞式結構FET」,和FinFET有相同的概念,不同之處在於此元件閘極圍繞了整個載子通道。依設計的不同,GAAFET可以以2個或4個等效閘極。此元件已經藉著利用矽奈米線和蝕刻砷化鎵銦(InGaAs)納米線被建造成功。

簡略模型

編輯UC Berkeley BSIM Group在2012年3月1號正式發表BSIMCMG106.0.0,這是第一個FinFET的標準模型。BSIM-CMG被實現在Verilog-A上。對於有限體參雜(body doping)的本質與非本質模型的物理面電勢公式皆已被導出。考慮了多消耗以及量子效應的源極和汲極端的面電勢也已明確地被導出來。透過微擾近似,我們已經可以理解有限體參雜的效應。導出的面電勢也與2-D元件的模擬相當接近。如果通道的參雜濃度很低,低到可以忽略,那麼在特殊情況下,我們可以更進一步改進計算效率。

所有重要的閘極電晶體的效應都已經被這個模型所捕捉。體積翻轉效應被包含在泊松方程的解裡,於是其後的I-V式子自然而然反映出了此效應。多閘極電晶體的電氣準電勢的分析給了如何解釋短通道效應的模型。這個模型包含了如何去控制多餘的閘電極(上/下閘電極)。

參見

編輯註釋

編輯- ^ Risch, L. "Pushing CMOS Beyond the Roadmap", Proceedings of ESSCIRC, 2005, p. 63.

- ^ Table39b (PDF). [2017-02-25]. (原始內容存檔 (PDF)於2007-09-27).

- ^ 3N201 (Motorola) - Dual Gate Mosfet Vhf Amplifier. Doc.chipfind.ru. [2014-03-10]. (原始內容存檔於2020-04-09).

- ^ 3SK45 datasheet pdf datenblatt - Hitachi Semiconductor - SILICON N-CHANNEL DUAL GATE MOSFET. Alldatasheet.com. [2014-03-10]. (原始內容存檔於2020-04-09).

- ^ BF1217WR (PDF). [2015-05-10]. (原始內容 (PDF)存檔於2020-04-09).

- ^ 劉金智潔 教授. 臺灣科學特殊人才提升計畫. [2023-01-28]. (原始內容存檔於2023-01-28).