數據選擇器

在電子技術(特別是數字電路)中,數據選擇器(英語:Data Selector),或稱多路復用器(英語:multiplexer,簡稱:MUX[1]),是一種可以從多個模擬或數字輸入信號中選擇一個信號進行輸出的器件。[2] 一個有 2n 輸入端的數據選擇器有 n 個可選擇的輸入-輸出線路,可以通過控制端來選擇其中一個信號被選擇作為輸出。[3] 數據選擇器主要用於增加一定量的時間和帶寬內的可以通過網絡發送的數據量。[2]

數據選擇器使多個信號共享一個設備或資源,例如一個模擬數字轉換器或一個傳輸線,而不必給每一個輸入信號配備一個設備。

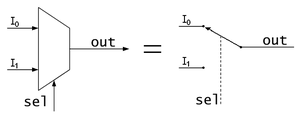

結構圖

編輯在結構圖中,數據選擇器的符號是一個等腰梯形,其中較長的底上為數個輸入引腳,較短的底上為一個輸出引腳。右圖即為一個2選1數據選擇器的結構圖和其等效簡化圖。Sel引腳可以選擇需要的信號。

此外,在很多數據選擇器里,還有一個「使能」引腳用於控制器件的有效或者無效[4]。

數字電路中的應用

編輯在數字電路設計中,選擇端的輸入信號是數字信號。在2選1數據選擇器的例子中,選擇端輸入低電平0,則輸出引腳會輸出 上的輸入信號;反之,當選擇端輸入高電平1,則輸出引腳會輸出 上的輸入信號。當輸入引腳的數目更多時,情況與上面類似,不過所需的選擇端引腳數目變為 個,這裡 是輸入引腳的個數。

一個2選1數據選擇器有如下的布爾函數, 和 分別表示兩個輸入信號, 為選擇信號, 為輸出信號,則有

注意,並非所有的邏輯函數直接具有以上的形式,但是所有的邏輯函數都可以使用香農展開(Shannon's expansion)的方法將它變換為上面這種形式。邏輯函數 可以用下面的真值表表示:

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | |

| 0 | 1 | 0 | |

| 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | |

| 0 | 1 | 1 | |

| 0 | 0 | 0 |

這個真值表顯示,當 ,那麼 ;而當 ,則 。在具體的電路中,實現一個這樣的2選1數據選擇器需要2個與門、一個或門和一個非門。

更大型的數據選擇器也較常見,而且正如上面描述的, 個輸入引腳需要 個選擇引腳。其他常見的類型有4選1、8選1和16選1等。由於數字邏輯採用二進制的數字信號,輸入引腳的個數通常是2的冪。

-

4選1數據選擇器

-

8選1數據選擇器

-

16選1數據選擇器

4選1數據選擇器的布爾函數如下:

這樣的數據選擇器可以由如下的電路實現:

| |||

芯片的級聯

編輯大型的數據選擇器可以由較小的數據選擇器級聯來實現[5]。例如,一個8選1數據選擇器可以由兩個4選1數據選擇器組成,一個4選1數據選擇器可以由兩個2選1數據選擇器組成。在前者中,兩個4選1選擇器的輸出端連接到2選1選擇器,並且兩個4選1選擇器和一個2選1選擇器的選擇端的引腳平行地接出,視為「8選1數據選擇器」的「3個選擇引腳」。

數據選擇集成芯片

編輯7400系列有若干種集成電路具有數據選擇器功能,列表如下[6]:

| IC 芯片代號 | 功能 | 輸出狀態 | |

|---|---|---|---|

| 1 | 74157 | 四2選1數據選擇器 | 輸出原變量 |

| 2 | 74158 | 四2選1數據選擇器 | 輸出反變量 |

| 3 | 74153 | 雙4選1數據選擇器 | 輸出原變量 |

| 4 | 74352 | 雙4選1數據選擇器 | 輸出反變量 |

| 5 | 74151A | 8選1數據選擇器 | 輸出原變量/反變量 |

| 6 | 74151 | 8選1數據選擇器 | 輸出反變量 |

| 7 | 74150 | 16選1數據選擇器 | 輸出反變量 |

數據選擇器作為可編程邏輯器件

編輯數據選擇器同樣可被用作可編程邏輯器件。通過指定輸入信號的排列,用戶可以創建一個定製的邏輯電路。選擇引腳充當了邏輯輸入的功能。當生產成本和模塊化有限的時候,這種方式十分有用。

在硬件描述語言中,可以採用數據流或者行為語句對數據選擇器進行描述。例如,在Verilog中,可以使用條件運算符条件?表达式1:表达式2或者使用if條件結構或case選擇結構來實現數據選擇器。

參考文獻

編輯- ^ What is a Multiplexer. wiseGEEK. [2011-04-22]. (原始內容存檔於2011-04-23).

- ^ 2.0 2.1 Dean, Tamara. Network+ Guide to Networks. Delmar. 2010: 82–85 [2015-04-04]. (原始內容存檔於2014-07-08).

- ^ Debashis, De. Basic Electronics. Dorling Kindersley. 2010: 557 [2015-04-04]. (原始內容存檔於2014-02-22).

- ^ 劉寶琴、王德生、羅嶸. 逻辑设计与数字系统. 北京: 清華大學出版社. : 61頁. ISBN 978-7-302-09320-6 (中文(中國大陸)).

- ^ 劉寶琴、王德生、羅嶸. 逻辑设计与数字系统. 北京: 清華大學出版社. : 62頁. ISBN 978-7-302-09320-6 (中文(中國大陸)).

- ^ 7400 Series Description. capetronics.com. (原始內容存檔於2010-02-13).

- M. Morris Mano; Charles R. Kime. Logic and Computer Design Fundamentals 4. Prentice Hall. 2008. ISBN 013198926X (英語).