多线程

此条目需要补充更多来源。 (2009年12月17日) |

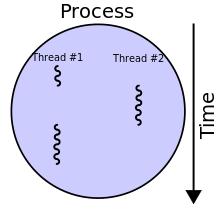

多线程(英语:multithreading),是指从软件或者硬件上实现多个线程并发执行的技术。具有多线程能力的电脑因有硬件支持而能够在同一时间执行多于一个线程,进而提升整体处理性能。具有这种能力的系统包括对称多处理机、多核心处理器以及晶片级多处理(Chip-level multithreading)或同时多线程(Simultaneous multithreading)处理器。

| “多线程”的各地常用名称 | |

|---|---|

| 中国大陆 | 多线程 |

| 台湾 | 多线、多执行绪 |

| 港澳 | 多线程 |

软件多线程。即便处理器只能运行一个线程,操作系统也可以通过快速的在不同线程之间进行切换,由于时间间隔很小,来给用户造成一种多个线程同时运行的假象。这样的程序运行机制被称为软件多线程。如微软的Windows作业系统和Linux就是在各个不同的线程间来回切换,被称为单人多工作业系统。而DOS这类文字接口作业系统在一个时间只能处理一项工作,被视为单人单工作业系统。

除此之外,许多系统及处理器也支持硬件多线程技术。对称多处理机(SMP)系统具有多个处理器,所以具有真正的同时执行多个线程的能力;CMP技术通过在一块晶片上集成多个核心(Core)也具有真正的多线程能力;CMT技术则稍有不同,有的是依靠硬件执行线程切换来获得多线程能力,操作系统不再负责线程切换,因而这部分开销可以减少甚至消除,这方面典型的例子是Sun的UltraSPARC T1,它同时综合了CMP和CMT。微软的Windows 2000以后的操作系统皆支持多线程与超线程技术。

概观

编辑由于程序代码中存在的数据及控制依赖关系,单线程中所能发掘的指令并行潜力是有限的。为了发掘有限的指令级并行潜力而一味强化乱序执行和分支预测,以至于处理器复杂度和功耗急剧上升,有时候是得不偿失的。因此,现代微处理器多采用硬件多线程技术来发掘线程之间的线程级并行潜力。这样子允许在接口转换的专业领域之运算能力大幅提升:

- 既使这样做对于提升单一程序或是线程的性能相当困难,但是目前多数的系统都是使用多工的方式作业。

- 能够明显的提升整体系统运算能力,总体吞吐量获得提升。

有两种提升运算能力的主要技术分别是多进程与多线程。

不过有些对多线程的批评如下:

粗粒度交替多线程

编辑概念

编辑一个线程持续执行,直到该线程被一个事件挡住而制造出长时间的延迟(可能是内存load/store操作,或者程序分支操作)。该延迟通常是因缓存失败而从核心外的内存读写,而这动作会使用到几百个CPU周期才能将资料回传。与其要等待延迟的时间,线程化处理器会切换执行到另一个已就绪的线程。只要当之前线程中的资料送达后,上一个线程就会变成已就绪的线程。这种方法来自各个线程的指令交替执行,可以有效的掩盖内存存取时延,填补流水线空洞。

举例来说:

- 周期 i :接收线程 A 的指令 j

- 周期 i+1:接收线程 A 的指令 j+1

- 周期 i+2:接收线程 A 的指令 j+2,而这指令缓存失败

- 周期 i+3:线程调度器介入,切换到线程 B

- 周期 i+4:接收线程 B 的指令 k

- 周期 i+5:接收线程 B 的指令 k+1

在概念上,它与即时操作系统中使用的合作式多工类似,在该任务需要为一个事件等待一段时间的时候会主动放弃执行时段。

硬件成本

编辑此种多线程硬件支持的目标,是允许在挡住的线程与已就绪的线程中快速切换。为了要达成这个目标,硬件成本将复制程序看得见的寄存器与一些处理器控制寄存器(像是程序计算器)。从一个线程切换到另一个线程对硬件来讲意谓著从一个寄存器复制到另一个。

这些新增功能的硬件有这些优势:

- 线程切换能够在一个 CPU 周期内完成(实际上可以没有开销,上个周期在运行线程A,下个周期就已在运行线程B)。

- 这样子看起来像是每个线程是独自执行的,没有其他线程与目前共享硬件资源。对操作系统来说,通常每个虚拟线程都被视做一个处理器。这样就不需要很大的软件变更(像是特别写支持多线程的操作系统)。

为了要在各个现行中的线程有效率的切换,每个现行中的线程需要有自己的暂存设置(register set)。像是为了能在两个线程中快速切换,硬件的寄存器需要两次例示(instantiated)。

示例

编辑细粒度交替式多线程

编辑概念

编辑另一种更高性能的多线程做法是将所有 CPU 周期轮流切换至不同的线程,来自各线程的指令按顺序交替执行。执行过程很像桶形处理器(Barrel Processor)就像这样:

- 周期 i :接收线程 A 的一个指令

- 周期 i+1:接收线程 B 的一个指令

- 周期 i+2:接收线程 C 的一个指令

这种线程的效果是会将所有从执行流水线中的资料从属(data dependency)关系移除掉。因为每个线程是相对独立,流水线中的一个指令层次结构需要从已跑完流水线中的较旧指令代入输出的机会就相对的变小了。

而在概念上,这种多线程与操作系统的核心先占多工(pre-exemptive multitasking)相似。

硬件成本

编辑除了讨论块状多线程的硬件成本,交错式多线程也因每层流水线需要追踪执行中指令的线程代码而增加硬件成本。而且,当越来越多的线程同时在流水线中执行,像是缓存与 TLB 等共享资源也要加大来避免不同线程之间的冲突。

示例

编辑- Denelcor Heterogeneous Element 处理器 (HEP)

- Intel Super-threading

- 昇阳 UltraSPARC T1

- Lexra NetVortex

- 搭载 Multi-Threaded ASE 的 MIPS 34K 核心

- Raza Microelectronics Inc XLR

同步多线程

编辑概念

编辑目前最先进的多线程技术是应用在超标量处理器上。超标量处理器内在每个CPU周期中,单独一个线程会发布众多的指令。套用同步多线程(SMT)之后,超标量处理器就可以在每个CPU周期中,从多个线程中发布指令。识别到任何一个单一线程拥有有限数量的指令平行处理,这种类型的多线程是试着利用并行的方式跨越多线程,以减少浪费与闲置的资源。 举例来说:

- 周期 i:线程 A 的 j 指令 与 j+1 指令,还有 B 线程的指令 k 同时发布

- 周期 i+1:线程 A 的 j+2 指令、线程 B 的 k+1指令,与线程 C 的 m 指令同时发布

- 周期 i+2:线程 A 的 j+3 指令,与线程 C 的 m+1 与 m+2 指令同时发布

硬件成本

编辑交错式多线程如果不计硬件成本,SMT在每个流水线层次结构的追踪线程指令会有多余的花费。而且,像是缓存与TLB这类共享的资源可能会因为多出来的线程而变得更大。

示例

编辑实现

编辑在大多数研究领域内是要求线程调度器要能够快速选择其中一个已就绪线程去执行,而不是一个一个执行而降低效率。所以要让调度器去分辨线程的优先级是很重要的。而线程调度器可能是以硬件、软件,或是软硬件并存的形式存在。

而另一个研究领域则是要研究何种事件(缓存失败、内部执行续连系、使用DMA等)会造成线程切换。

如果多线程的方案会复制所有软件可见的状态,包括特许的控制登录、TLB 等,那就能够让虚拟机去创造各式线程。这样子就允许在相同的处理器中每个线程跑各自的操作系统。换句话说,如果只有存储了用户模式的状态,就能够让相同的裸晶大小的晶片在一段时间内处理更多的线程。

参见

编辑外部链接

编辑- 兼听则明—从CMT与SMT技术之争谈起

- 全方位了解服务器CPU【技术篇】(页面存档备份,存于互联网档案馆)

- 精彩图解服务器CPU(页面存档备份,存于互联网档案馆)

- 提高处理器的吞吐量(IMPROVING THROUGHPUT)(页面存档备份,存于互联网档案馆)