電子設計自動化

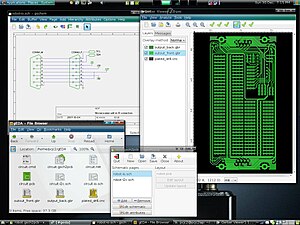

電子設計自動化(英語:Electronic design automation,縮寫:EDA)是指利用計算機輔助設計(CAD)軟體,來完成超大型積體電路(VLSI)晶片[來源請求]的功能設計、綜合、驗證、物理設計(包括布局、布線、版圖、設計規則檢查等)等流程的設計方式。

歷史與發展

編輯在電子設計自動化出現之前,設計人員必須手工完成積體電路的設計、布線等工作,這是因為當時所謂積體電路的複雜程度遠不及現在。工業界開始使用幾何學方法來製造用於電路光繪(photoplotter)的膠帶。[來源請求]

到了1970年代中期,開發人員嘗試將整個設計過程自動化,而不僅僅滿足於自動完成掩膜草圖。第一個電路布局、布線工具研發成功。設計自動化研討會(Design Automation Conference)在這一時期被創立,旨在促進電子設計自動化的發展。[1]

電子設計自動化發展的下一個重要階段以卡弗爾·米德(Carver Mead)和琳·康維於1980年發表的論文《超大型積體電路系統導論》(Introduction to VLSI Systems)為標誌。這一篇具有重大意義的論文提出了通過程式語言來進行晶片設計的新思想。[2]如果這一想法得到實現,晶片設計的複雜程度可以得到顯著提升。這主要得益於用來進行積體電路邏輯仿真、功能驗證的工具的性能得到相當的改善。隨著計算機仿真技術的發展,設計項目可以在構建實際硬體電路之前進行仿真,晶片布局、布線對人工設計的要求降低,而且軟體錯誤率不斷降低。直至今日,儘管所用的語言和工具仍然不斷在發展,但是通過程式語言來設計、驗證電路預期行為,利用工具軟體綜合得到低抽象級(或稱「後端」)物理設計的這種途徑,仍然是數位積體電路設計的基礎。

從1981年開始,電子設計自動化逐漸開始商業化。1984年的設計自動化會議(Design Automation Conference)上還舉辦了第一個以電子設計自動化為主題的銷售展覽。Gateway設計自動化在1986年推出了一種硬體描述語言Verilog,這種語言在現在是最流行的高級抽象設計語言。[3][4]1987年,在美國國防部的資助下,另一種硬體描述語言VHDL被創造出來。現代的電子設計自動化設計工具可以識別、讀取不同類型的硬體描述。[5]根據這些語言規範產生的各種仿真系統迅速被推出,使得設計人員可對設計的晶片進行直接仿真。後來,技術的發展更側重於邏輯綜合。

進入21世紀之後,一方面,三家大EDA公司(Synopsys、Cadence、Mentor)通過多次併購整合,完善設計全流程,奠定了三巨頭競爭格局。另一方面,EDA公司開始深入製造領域,發展出了OPC等製造EDA的工具以及可製造性設計(DFM)工具。同時,晶圓廠成為了EDA的深度用戶,不僅在製造方面需要使用EDA工具,在標準單元庫、SRAM設計上都需要使用。此外,領先晶圓廠每兩年開發一代製程,其中EDA的整套設計流程需要在新製程上驗證。EDA也開始在早期製程研發中介入,幫助解決更複雜的設計規則以及種種難題。晶圓廠提供的Signoff簽核流程決定了設計公司設計出的晶片能否在晶圓製造廠順利生產。而Signoff簽核的主要工具就是EDA,可以說EDA是架起了設計與製造溝通的橋梁。同時,先進製程不斷迭代也驅動了EDA的創新。可見,此時此刻EDA在產業鏈已經有著舉足輕重的作用。[6]

目前的數位積體電路的設計都比較模組化(參見積體電路設計、設計收斂(Design closure)和設計流(Design flow (EDA))。半導體元件製造製程需要標準化的設計描述,高抽象級的描述將被編譯為信息單元(cell)的形式。設計人員在進行邏輯設計時尚無需考慮信息單元的具體硬體製程。利用特定的積體電路製造製程來實現硬體電路,信息單元就會實施預定義的邏輯或其他電子功能。半導體硬體廠商大多會為它們製造的元件提供「元件庫」,並提供相應的標準化仿真模型。相比數位的電子設計自動化工具,類比系統的電子設計自動化工具大多並非模組化的,這是因為類比電路的功能更加複雜,而且不同部分的相互影響較強,而且作用規律複雜,電子元件大多沒有那麼理想。Verilog AMS就是一種用於類比電子設計的硬體描述語言。[7]此外,設計人員可以使用硬體驗證語言來完成項目的驗證工作目前最新的發展趨勢是將集描述語言、驗證語言集成為一體,典型的例子有SystemVerilog。[8][9]

隨著積體電路規模的擴大、半導體技術的發展,EDA的重要性急劇增加。這些工具的使用者包括半導體元件製造中心的硬體技術人員,他們的工作是操作半導體元件製造設備並管理整個工作車間。一些以設計為主要業務的公司,也會使用電子設計自動化軟體來評估製造部門是否能夠適應新的設計任務。電子設計自動化工具還被用來將設計的功能導入到類似現場可程式化邏輯閘陣列的半定製可程式邏輯裝置,或者生產全定製的特殊應用積體電路。

現況

編輯現今數位電路非常模組化(參見積體電路設計、設計收斂、設計流程 (EDA)),產線最前端將設計流程標準化,把設計流程區分為許多「細胞」(cells),而暫不考慮技術,接著細胞則以特定的積體電路技術實現邏輯或其他電子功能。製造商通常會提供組件庫(libraries of components),以及符合標準類比工具的類比模型給生產流程。類比EDA工具較不模組化,因為它需要更多的功能,零件間需要更多的互動,而零件一般說較不理想。

在電子產業中,由於半導體產業的規模日益擴大,EDA扮演越來越重要的角色。使用這項技術的廠商多是從事半導體元件製造的代工製造商,以及使用EDA類比軟體以評估生產情況的設計服務公司。EDA工具也應用在現場可程式化邏輯閘陣列的程式設計上。

如今的積體電路,從系統架構開始,落實到功能的定義和實現,最終實現整個晶片的版圖設計與驗證,是一項複雜的系統工程,集成了人類智慧的最高成果。以華為2020年最新的7nm麒麟990晶片來說,其中集成了103億顆電晶體,若沒有EDA輔助,設計這樣複雜的電路並保證良率是無法想像的。可見EDA這套工具,賦能了積體電路設計與製造的創新,當之無愧的站在了產業鏈的頂端。[6]

未來發展趨勢

編輯目前,EDA在國際市場上已經發展成為了相對成熟的產業,而每年增長率只有10%左右。[6]但有業內人士分析認為,這並不代表日後發展的機會在變小,在未來 EDA 的發展趨勢可能有:[6]

- AI賦能

- EDA上雲

- 異構集成

重點軟體分類

編輯設計

編輯- 高級綜合(或行為綜合、算法綜合)——高級設計描述(例如在C/C++中)轉換為RTL。

- 邏輯綜合-將RTL設計描述(例如用Verilog或VHDL編寫)轉換為邏輯閘的離散netlist。

- 原理圖捕獲-用於標準單元數位,類比,rf類捕獲CIS在Orcad由Cadence和ISIS在Proteus

- 布局——通常是由模式驅動的布局,比如在Orcad中的Cadence布局,在Proteus中的ARES布局

仿真

編輯- 電晶體仿真——對原理圖/布局行為的低層電晶體仿真,精確到元件級別。

- 邏輯仿真——對RTL或閘網表的數位行為進行數位仿真,精確到布林級別。

- 行為仿真——對設計的架構操作進行高層仿真,精確到周期級別或介面級別。

- 硬體仿真——使用特殊目的硬體仿真擬議設計的邏輯,有時可以插入到系統中替代尚未構建的晶片;這被稱為電路仿真。

- 技術CAD仿真和分析基礎過程技術。元件的電氣特性直接從元件物理推導。

分析及驗證

編輯- 功能驗證:確保邏輯設計與規格相符,並正確執行任務。包括通過仿真、仿真和原型的動態功能驗證。

- RTL Linting:檢查代碼是否遵循語法、語義和樣式等編碼規則。

- 時鐘域交叉驗證(CDC檢查):類似於Linting,但這些檢查/工具專門用於檢測和報告由於使用多個時鐘域而可能出現的數據丟失、元穩定性等問題。

- 形式驗證,也稱為模型檢查:嘗試通過數學方法證明系統具有某些期望的屬性,並且某些不希望發生的效果(如死鎖)不會發生。

- 等效性檢查:對晶片的RTL描述和綜合後的門網表進行算法比較,以確保邏輯層面的功能等效。

- 靜態時序分析:以輸入無關的方式分析電路的時序,從而找到所有可能輸入的最壞情況。

- 布局提取:從擬議的布局開始,計算每條導線和元件的(近似)電氣特性。通常與上述靜態時序分析一起使用,以估算完成晶片的性能。

- 電磁場求解器,或稱場求解器,直接求解麥克斯韋方程,適用於積體電路和PCB設計中的特定問題。它們以精確度較高、但速度較慢而聞名。

- 物理驗證,PV:檢查設計是否可以物理製造,生成的晶片是否不存在任何阻止功能的物理缺陷,並且能滿足原始規格。

製造製備

編輯- 光罩數據準備或MDP——生成實際的微影光罩,用於物理製造晶片。

- 晶片修整,包括定製設計標記和結構,以提高布局的可製造性。後者的例子包括密封環和填充結構。

- 生成帶有測試圖案和對準標記的光罩布局。

- 布局到光罩準備:通過圖形操作增強布局數據,如解析度增強技術(RET)——提高最終微影光罩的質量的方法。還包括光學鄰近效應修正(OPC)或逆微影技術(ILT)——在晶片製造時補償衍射和干涉效應。

- 光罩生成——從分層設計生成平面光罩圖像。

- 自動測試圖案生成或ATPG——系統地生成模式數據,以儘可能多地測試邏輯閘和其他組件。

- 自測試或BIST——安裝自包含的測試控制器,自動測試設計中的邏輯或存儲器結構。

- 功能安全

- 功能安全分析,系統地計算設計中的失效率(FIT)和診斷覆蓋度指標,以滿足所需的安全完整性級別的合規性要求。

- 功能安全綜合,通過在結構化元素(模塊、RAM、ROM、暫存器文件、FIFO)中增加可靠性增強來改善故障檢測/容錯能力。這包括(但不限於)添加錯誤檢測和/或糾正代碼(漢明碼)、冗餘邏輯用於故障檢測和容錯(雙重/三重)以及協議檢查(介面奇偶校驗、地址對齊、節拍計數)。

- 功能安全驗證,運行故障試驗,包括向設計中插入故障並驗證安全機制對已覆蓋的故障作出適當反應。

參見

編輯參考文獻

編輯- ^ Access Years of Vital Information. DAC. [2013-01-05]. (原始內容存檔於2013-09-29).

- ^ Carver Mead, Lynn Conway. Introduction to VLSI Systems. Addison-Wesley Pub (Sd). 1980. ISBN 978-0201043587.

- ^ Donald E. Thomas, Philip R. Moorby. 硬件描述语言Verilog(第四版,英文名:The Verilog Hardware Description Language (Fouth Edition)). 清華大學出版社. 2001. ISBN 7-900635-36-X.

- ^ 夏宇聞. Verilog基本知识 (上). 電子產品世界. 2002, (19).

- ^ Mixed VHDL/Verilog Synthesis. University of Edinburgh. [2012-08-15]. (原始內容存檔於2013-06-11).

- ^ 6.0 6.1 6.2 6.3 韓明. EDA发展要秉持“战略冗余”观念 (PDF). 中國電子報 (總第4358期) (中國電子報社). 2020年6月19日 [2020年6月19日]. (原始內容 (PDF)存檔於2020年6月22日).

- ^ 夏宇聞. 一种高层次的支持模拟和数模混合信号电路与系统设计的语言Verilog-A/AMS. 電子技術應用. 1999, 25 (8).

- ^ 1800-2009 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language. IEEE. [2012-08-13]. (原始內容存檔於2012-05-07).

- ^ SystemVerilog Overview. SystemVerilog Official Website. [2012-08-24]. (原始內容存檔於2012-05-02).

- Steven M. Rubin. Computer Aids for VLSI Design. Static Free Software. [2013-01-05]. (原始內容存檔於2020-09-24).

- Lavagno, Martin, and Scheffer. Electronic Design Automation For Integrated Circuits Handbook. CRC Press. 2006. ISBN 0-8493-3096-3.

- Thomas Lengauer. Combinatorial Algorithms for Integrated Circuit Layout. Teubner Verlag. 1997. ISBN 3-519-02110-2.

- Dirk Jansen; et al. The Electronic Design Automation Handbook. Kluwer Academic Publishers. 2003. ISBN 1-4020-7502-2.