與非門

| NAND 邏輯門 | ||

|---|---|---|

| 輸入 | 輸出 | |

| A | B | A NAND B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

與非門(英語:NAND gate)是數碼邏輯中實現邏輯與非的邏輯門。若輸入均為高電平(1),則輸出為低電平(0);若輸入中至少有一個為低電平(0),則輸出為高電平(1)。與非門是一種通用的邏輯門,因為任何布林函數都能用與非門實現。

使用特定邏輯電路的數碼系統利用了與非門的函數完備性(功能完備性)。複雜的邏輯表達式常以其他邏輯函數表示,如與、或、非,而將表達式改寫為用邏輯與非表示的式子可以節約成本,因為使用與非門實現電路能使電路結構更為緊湊。

與非門並不僅限於2輸入,可以是多輸入,這時當輸入全為高電平時,輸出為低電平;若有任意一個輸入為低電平,則輸出為高電平。這些門電路不再是簡單的二進制運算器,而是可作為n元運算器使用的門電路。代數中,這些門電路可以用函數NAND(a, b, ..., n)表示,等價於NOT(a AND b AND ... AND n)。

概述

編輯| 輸入 A B |

輸出 A NAND B | |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

下列包括邏輯門的3種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)和不再使用的DIN符號(DIN 40700)。其他的邏輯門符號見邏輯門符號表。

| 表達式 | 符號 | 功能表 | 繼電器邏輯 | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||||||||||||

| |

|

|||||||||||||||||||

硬件描述和引腳分配

編輯與非門是基本的門電路,因此常用於電晶體-電晶體邏輯(TTL)和CMOS集成電路。

TTL版本

編輯與非門是TTL中最基本、電路最簡單的多輸入邏輯門,在TTL電路中扮演重要角色。 7400內含四組2輸入與非門,是TTL編號中排在第一的型號。

CMOS版本

編輯標準4000系列CMOS集成電路為4011,包含4個獨立的2端輸入與非門。

可用型號

編輯大多數半導體製造商都生產這種元件,如快捷半導體公司、飛利浦、德州儀器,封裝方式分為雙列直插封裝和SOIC封裝兩種。元件的數據表可在大多數元件數據庫查詢到。

下列是可以獲得的標準2、3、4、8輸入與非門型號:

實現

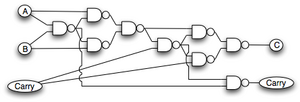

編輯與非門具有函數完備性,因此其他的邏輯功能(與、非等)都可以僅用與非門來實現。一個完整的處理器可以只用與非門製作出來。在使用多射極電晶體的TTL集成電路中,與非門需要的電晶體也少於其他任何門電路。

應用

編輯與非門是數碼電子技術中最重要的邏輯門,可組成加法器、數據多工器等組合邏輯電路,而且由於其完備性,可以僅用其組成電路,有利於電路的集成,能使集成電路的造價降低很多。

與非邏輯

編輯| 運算 | 實現 |

|---|---|

| NOT x | x NAND x |

| x AND y | (x NAND y) NAND (x NAND y) |

| x NAND y | x NAND y |

| x OR y | (x NAND x) NAND (y NAND y) |

| x NOR y | ((x NAND x) NAND (y NAND y)) NAND ((x NAND x) NAND (y NAND y)) |

| x XOR y | (x NAND (y NAND y)) NAND ((x NAND x) NAND y) |

| ((x NAND y) NAND y)) NAND ((x NAND y) NAND x)) | |

| x XNOR y | (x NAND y) NAND ((x NAND x) NAND (y NAND y)) |

| ≡ x ⇔ y | |

| x ⇒ y | x NAND (y NAND y) |

| x ⇐ y | (x NAND x) NAND y |

| x ⇔ y | (x NAND y) NAND ((x NAND x) NAND (y NAND y)) |

| ≡ x XNOR y | |

| 重言式 | (x NAND x) NAND x |

| 矛盾式 | ((x NAND x) NAND x) NAND ((x NAND x) NAND x) |

參見

編輯